技术文章

Technical articles 热门搜索:

P760/01_2760nm单模垂直腔面发射激光器

RFLDM-RF射频激光二极管驱动(控制/电源)

ZNSP25.4-1IR抛光硫化锌(ZnS)多光谱(透明)窗片 0.37-13.5um 25.4X1.0mm(晶体/棱镜

2x4 QPSK C波段相干混频器(信号解调/锁相放大器等)

Frequad-W-CW DUV 单频连续激光器 213nm 10mW Frequad-W

截止波长1300nm 高掺杂EDF掺铒光纤

SNA-4-FC-UPC日本精工法兰FC/UPC(连接器/光纤束/光缆)

GD5210Y-2-2-TO46905nm 硅雪崩光电二极管 400-1100nm

WISTSense Point 紧凑型高精度光纤传感器解调仪(信号解调/锁相放大器等)

CO2激光光谱分析仪

超高功率光束质量分析仪

350-2000nm 1倍红外观察镜

1030nm超短脉冲种子激光器PS-PSL-1030

NANOFIBER-400-9-SA干涉型单模微纳光纤传感器 1270-2000nm

高能激光光谱光束组合的光栅 (色散匀化片)

S+C+L波段 160nm可调谐带通滤波器

热门搜索:

P760/01_2760nm单模垂直腔面发射激光器

RFLDM-RF射频激光二极管驱动(控制/电源)

ZNSP25.4-1IR抛光硫化锌(ZnS)多光谱(透明)窗片 0.37-13.5um 25.4X1.0mm(晶体/棱镜

2x4 QPSK C波段相干混频器(信号解调/锁相放大器等)

Frequad-W-CW DUV 单频连续激光器 213nm 10mW Frequad-W

截止波长1300nm 高掺杂EDF掺铒光纤

SNA-4-FC-UPC日本精工法兰FC/UPC(连接器/光纤束/光缆)

GD5210Y-2-2-TO46905nm 硅雪崩光电二极管 400-1100nm

WISTSense Point 紧凑型高精度光纤传感器解调仪(信号解调/锁相放大器等)

CO2激光光谱分析仪

超高功率光束质量分析仪

350-2000nm 1倍红外观察镜

1030nm超短脉冲种子激光器PS-PSL-1030

NANOFIBER-400-9-SA干涉型单模微纳光纤传感器 1270-2000nm

高能激光光谱光束组合的光栅 (色散匀化片)

S+C+L波段 160nm可调谐带通滤波器

更新时间:2025-10-23

更新时间:2025-10-23 点击次数:792

点击次数:792

一.背景介绍

进入21世纪后,光子集成技术(PIC)逐渐成为备受关注的课题之一。原因无外乎两方面:其一,信息技术的应用达到了新的爆炸点,诸如大数据、人工智能、高速网络、虚拟现实、量子信息等等都对具有低能耗、超高算力、可高速重构的光子器件提出了迫切需求;其二,光子集成技术自身也在不断突破,片上器件的性能和成本不断降低,达到了驱动新产业生态的门槛。在这一背景下,薄膜铌酸锂逐渐成为一种重要的光子集成材料。

铌酸锂(LiNbO3)由于其优异的电光和非线性光学特性、相对较高的折射率和较宽的透明窗口,自20世纪60年代以来一直被广泛应用于光子学领域。近年来,随着通过离子切片制备的商业化薄膜铌酸锂晶圆的出现,以及加工制备技术的快速发展,基于薄膜铌酸锂平台[1]开发出了一系列光学器件,包括超低损耗可调光波导延时线、超高速光调制器、高效率量子光源,以及高功率片上放大器与片上激光器等。这些器件以其体积小、质量轻、功耗低、性能好的综合优势,在光通信、光量子信息处理、光传感和光学计算等领域具有广泛的应用前景。它们可以用于实现高速、高容量的光通信系统,提供更稳定和可靠的光量子信息处理,以及实现高精度的光传感和光学计算。

二.关键技术进展

(1)大尺寸光刻技术超低损耗波导加工工艺

多年来,随着对高密度集成的需求不断增加,制备高质量的铌酸锂薄膜以及在干法蚀刻过程中形成高质量的光子结构成为了一项巨大的挑战。在大规模的光子集成芯片器件中,实现超低损耗的波导对于获得令人满意的性能至关重要。

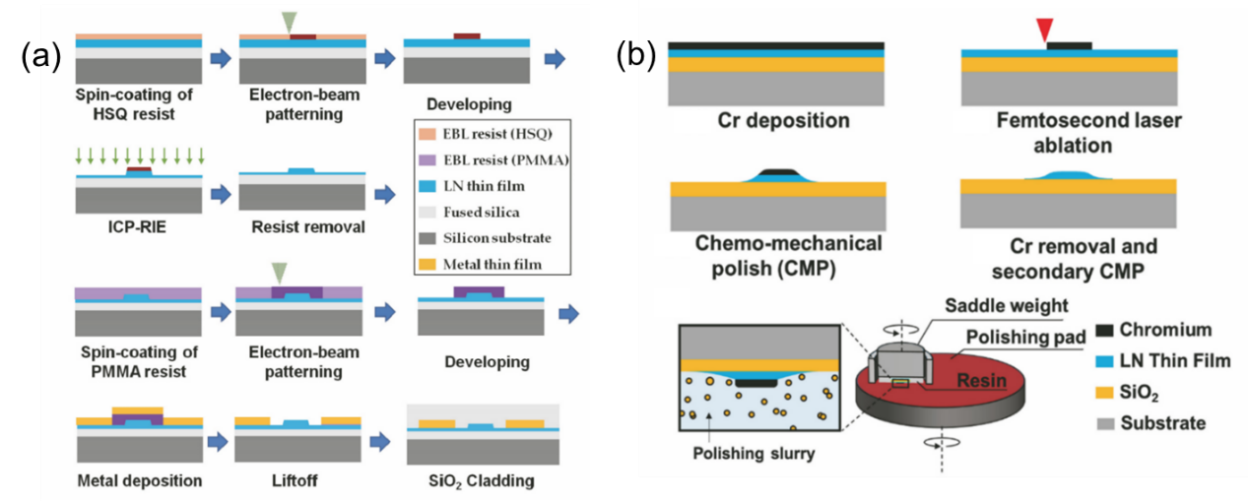

2014年,哈佛大学提出了电子束曝光结合离子刻蚀技术[2],该技术与成熟的互补金属氧化物半导体(CMOS)兼容,因此更易获得推广应用。如图1(a)所示,该制备技术路线的核心包括光刻胶曝光(光刻)和离子干法刻蚀两个主要步骤。通过该技术所制备的薄膜铌酸锂波导损耗可低至0.027 dB/cm[3],因而被广泛用于薄膜铌酸锂原型器件制造中。

2018年,中国科学院上海光机所与华东师范大学提出了飞秒激光直写辅助化学机械抛光(Photolithography Assisted Chemo-Mechanical Etching,PLACE)技术[4],目的是在薄膜铌酸锂上实现超低损耗光子器件和集成系统的晶圆级光刻制造。如图1(b)所示,PLACE技术利用飞秒激光直写来制备铬掩模,然后通过化学机械抛光来蚀刻铌酸锂。利用这项技术制备的波导损耗同样可以低至0.027 dB/cm[5]。PLACE技术的独特优势在于突破了单次连续曝光区域的尺寸限制,并可获得极低的波导传输损耗,这两项优势对于实现大规模铌酸锂光子芯片并推动其应用具有重要意义。

图1 (a)利用电子束曝光结合离子束刻蚀的方法制备薄膜铌酸锂光子结构的工艺流程示意图;(b)飞秒激光直写辅助化学机械抛光(PLACE)制备铌酸锂光子芯片的工艺流程图

(2)多功能可重构薄膜铌酸锂光子芯片

在光量子信息处理、量子增强传感器、光子神经网络等新兴应用中,由级联马赫-曾德尔干涉仪组成的可编程线性光子线路变得越发重要。这些新兴应用对超大规模光子集成和以具备极低损耗、超高开关速度的光调制器为代表的高性能片上组件提出了严格的要求。薄膜铌酸锂作为一种重要的光子集成材料,满足了可编程光子线路提出的所有严格的器件要求。

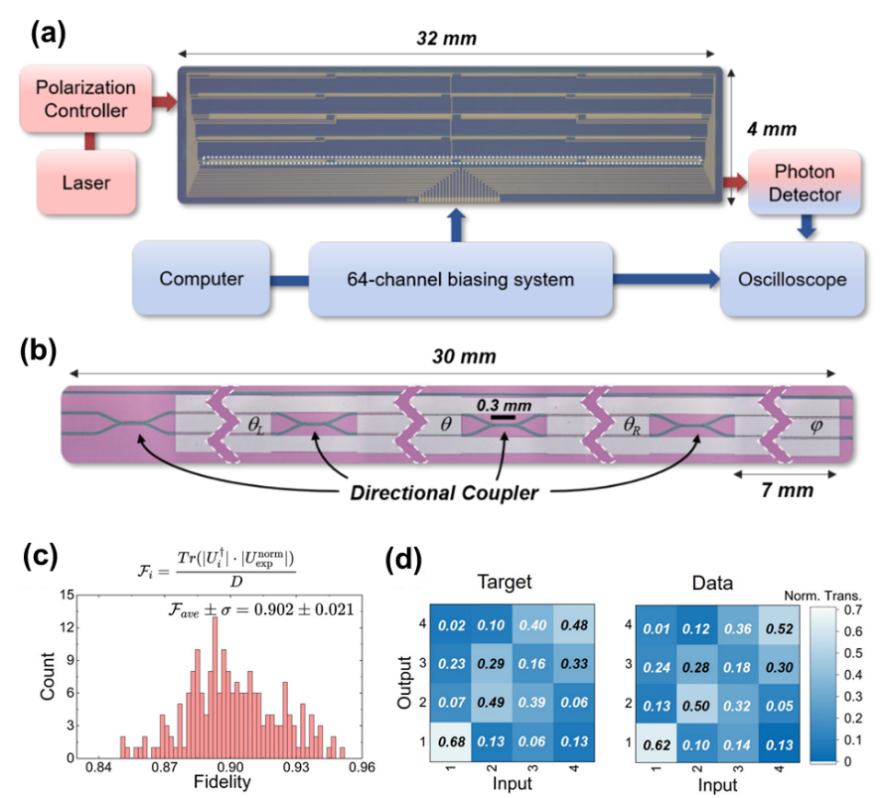

近期,华东师范大学、中国科学院上海光机所在薄膜铌酸锂衬底上实现了4×4可编程线性光子运算器[6]。该器件在损耗、功耗和运算速度方面显示出巨大优势。图2(a)展示了可编程线性光子运算器的照片,其中任意SU(4)变换由6个可重构的马赫-曾德尔干涉仪单元实现。每个马赫-曾德尔干涉仪单元的内部结构如图2(b)所示,其插损仅为0.15 dB。该器件在1 MHz调制率下执行运算时,片上总功耗仅为15 µW。如图2(c)中的直方图所示,利用该器件执行了200次随机4×4酉矩阵变换计算,得到的矩阵保真度为0.902±0.021。图2(d)直接对比了其中一个矩阵运算的理论结果和实验测量结果,大误差小于10%。这项工作为实现大规模、低功耗和高性能的光子芯片在前沿经典和量子应用中的应用迈出了重要的一步。

图2 基于薄膜铌酸锂平台制备的4×4可编程线性光子芯片[6]。(a)任意SU(4)变换矩阵;(b)MZI单元的内部结构;(c)200个随机矩阵的测量保真度的直方图;(d)其中一个矩阵的理论与实验结果的对比

(3)薄膜铌酸锂大规模光子集成

对于薄膜铌酸锂大规模光子集成,我们考虑一个适用于多种应用场景的代表性器件,并考察其制备可能性与性能极限。在这个假想器件中,我们通过将尽可能多的铌酸锂马赫-曾德尔干涉仪排列成一个网格阵列,放置在单个薄膜铌酸锂晶圆上构建光子集成器件[7]。

从技术上讲,由于4英寸的薄膜铌酸锂晶圆已经商业化可用,我们考虑在4英寸晶圆允许的60 mm×60 mm的方形区域内构建马赫-曾德尔干涉仪阵列。如图3(a)所示,在保障铌酸锂波导可承受的调制电压的前提下,薄膜铌酸锂上单个马赫-曾德尔干涉仪的尺寸可以小至0.2 mm×2.5 mm。通过PLACE技术,图3(b)所示,一个由7200个马赫-曾德尔干涉仪组成的光子器件将很容易实现。在这样一个大规模的光子集成芯片器件中,总传输损耗预计低可到0.5 dB。此外,如图3(c)所示,利用PLACE技术,我们能够以连续光刻方式单次加工预先拼接好的9片铌酸锂晶圆,实现超大规模铌酸锂光子集成器件的整体图案化。利用该连续光刻加工技术,可以自动确保不同晶圆中波导阵列间的高精度对准。终,该整体拼接的铌酸锂晶圆上的马赫-曾德尔干涉仪的总数可以达到64800个。

这一集成规模一旦实现,将会根本性地改变光子集成领域的状况,推动人类智能社会进入一个新的技术时代。这也是2017年,哈佛大学郑重宣告“Now entering, lithium niobate valley"(人类正在进入铌酸锂谷的时代)的信念来源。

图3(a)基于薄膜铌酸锂的马赫-曾德尔干涉仪的原理图;(b)4英寸晶圆上制备的7200个马赫-曾德尔干涉仪阵列组成的光子集成芯片示意图;(c)利用PLACE技术在9片4英寸晶圆中单次制备的64800个马赫-曾德尔干涉仪阵列组成的光子集成芯片示意图

三.总结与展望

集成光子技术长期受到片上光波导高传输损耗和高调制功耗的制约,无法持续扩大集成规模。近10年来,薄膜铌酸锂光子学的快速发展为改变这一现状提供了可能。薄膜铌酸锂结合优良的微纳光子制备技术,已经实现了光子集成领域的一系列突破,使得光子器件在调制带宽、调制功耗、传输损耗、有源无源集成、超大集成规模等方面都有显著提升。值得一提的是,目前这些性能大都还未达到铌酸锂光子器件的物理极限,因此,薄膜铌酸锂集成光子技术仍具有广阔的发展空间。同时,很多薄膜铌酸锂光子器件都已接近甚至具备了产业应用的条件,这将为下一代光信息技术发展提供强大驱动力。

参考文献: 中国光学期刊网

您好,可以免费咨询技术客服[Daisy]

筱晓(上海)光子技术有限公司

欢迎大家给我们留言,私信我们会详细解答,分享产品链接给您。

免责声明:

资讯内容来源于互联网,目的在于传递信息,提供专业服务,不代表本网站及新媒体平台赞同其观点和对其真实性负责。如对文、图等版权问题存在异议的,请联系我们将协调给予删除处理。行业资讯仅供参考,不存在竞争的经济利益。