技术文章

Technical articles 热门搜索:

P760/01_2760nm单模垂直腔面发射激光器

VCSEL-20-M激光控制驱动器

ZNSP25.4-1IR抛光硫化锌(ZnS)多光谱(透明)窗片 0.37-13.5um 25.4X1.0mm(晶体/棱镜

2x4 QPSK C波段相干混频器(信号解调/锁相放大器等)

Frequad-W-CW DUV 单频连续激光器 213nm 10mW Frequad-W

ER40-6/125截止波长1300nm 高掺杂EDF掺铒光纤

SNA-4-FC-UPC日本精工法兰FC/UPC(连接器/光纤束/光缆)

GD5210Y-2-2-TO46905nm 硅雪崩光电二极管 400-1100nm

WISTSense Point 紧凑型高精度光纤传感器解调仪(信号解调/锁相放大器等)

CO2激光光谱分析仪

超高功率光束质量分析仪

350-2000nm 1倍红外观察镜

1030nm超短脉冲种子激光器PS-PSL-1030

NANOFIBER-400-9-SA干涉型单模微纳光纤传感器 1270-2000nm

高能激光光谱光束组合的光栅 (色散匀化片)

S+C+L波段 160nm可调谐带通滤波器

热门搜索:

P760/01_2760nm单模垂直腔面发射激光器

VCSEL-20-M激光控制驱动器

ZNSP25.4-1IR抛光硫化锌(ZnS)多光谱(透明)窗片 0.37-13.5um 25.4X1.0mm(晶体/棱镜

2x4 QPSK C波段相干混频器(信号解调/锁相放大器等)

Frequad-W-CW DUV 单频连续激光器 213nm 10mW Frequad-W

ER40-6/125截止波长1300nm 高掺杂EDF掺铒光纤

SNA-4-FC-UPC日本精工法兰FC/UPC(连接器/光纤束/光缆)

GD5210Y-2-2-TO46905nm 硅雪崩光电二极管 400-1100nm

WISTSense Point 紧凑型高精度光纤传感器解调仪(信号解调/锁相放大器等)

CO2激光光谱分析仪

超高功率光束质量分析仪

350-2000nm 1倍红外观察镜

1030nm超短脉冲种子激光器PS-PSL-1030

NANOFIBER-400-9-SA干涉型单模微纳光纤传感器 1270-2000nm

高能激光光谱光束组合的光栅 (色散匀化片)

S+C+L波段 160nm可调谐带通滤波器

更新时间:2026-01-22

更新时间:2026-01-22 点击次数:321

点击次数:321

在 housing=55℃ 条件下,QSFP ELS 实现:

8×20 dBm(总0.8 W)

整机功耗 5.6 W

模块级 PCE 14.3%

图8给出 8 通道 TOSA 的实物照片。基板左侧通过 FPC(柔性电路板)与各通道 LD/PD实现电连接;基板右侧 8 根 PMF(保偏光纤)从 TOSA 的铝盖处引出。尾纤处有胶水保护。

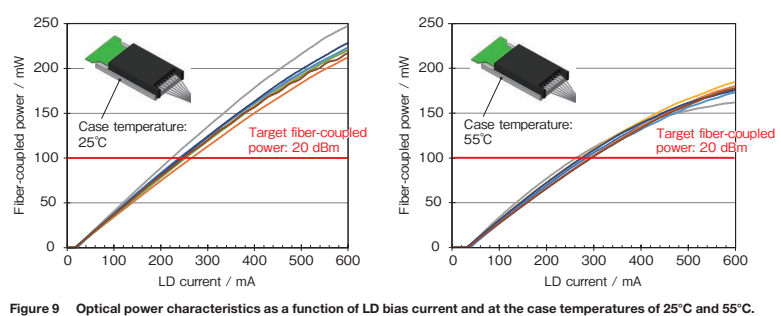

图9展示了 case=25℃ 与 55℃ 下,8 通道光纤耦合输出功率随 LD 偏置电流变化的曲线。结果表明:

为什么<300 mA很关键?(这句话直接与模块功耗 5.6 W强相关)

模块级功耗里有一大块来自供电链路:3.3 V → DC/DC → LD bias。当达到目标光功率所需电流更低时,意味着:

1)LD 本体电功耗更低(I 降了,I·V 自然下降);

2)DC/DC 的输出功率需求更低,转换损耗也跟着下降;

3)在 APC(恒功率)模式下,为补偿温漂所需的电流裕量更充足,更容易在 55℃ 仍把整机功耗压在 5–6 W 量级。

换句话说:这是 14.3% 模块级 PCE 能成立的先决条件之一。

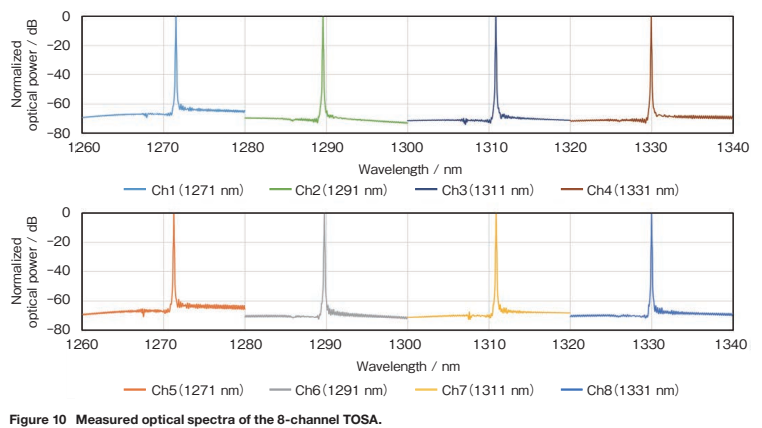

图10给出所有通道的实测光谱:

在 case=55℃ 下,该 TOSA 可实现全通道均达到 20 dBm 的光纤耦合输出,总光功率为:

Popt_total = 8 × 100 mW = 0.8 W

同时 TOSA 功耗低至:

Pin_TOSA = 3.7 W

因此 TOSA 级 PCE 为:

PCE_TOSA = 0.8 / 3.7 ≈ 21.2%

提醒:这里的 TOSA 级 PCE 不包含控制/驱动电路与 DC/DC 电源转换损耗;而后续 QSFP ELS 的 模块级 PCE(14.3%)是整机的,两者必须分开对比。

本节一句话结论:TOSA 作为光源引擎,在 55℃ case 下已经做到了高耦合(80–85%)+ 低电流(<300 mA)+ 干净光谱(SMSR>50 dB)+ 高效率(21.2%);后续任务是:把它装进 QSFP 后仍然守住这些输入条件,并把系统损耗压到足够低,让模块级 PCE 站得住。

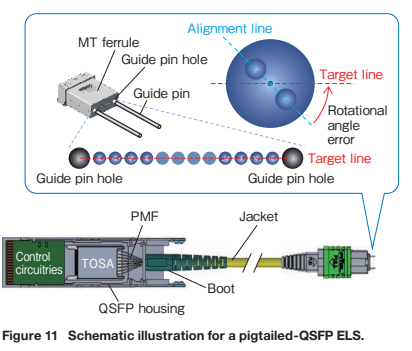

他们在 MT/MPO 端面建立两个参考线:

Target line(目标线)

Alignment line(对准线)

补充:

1、采用业内常用的芳纶压接结构,其抗拉本质是芳纶接管拉力路径,避免拉力传递到裸纤;

BOOT 的限位结构则用于阻断外部弯折/拖拽应力向内传递。

本小节一句话:先建立参考系,再谈 PER 才能量产。

结论先行:模块级 PCE 想高,关键在供电电压贴近需求,减少压差损耗。

作者给出控制电路框图,其中省电关键在 DC/DC:

在较小压差下提供所需偏置电流(文中提到可支持到 500 mA 级)

控制方式上:

ACC(恒流):简单,但输出易随温度/老化漂

APC(恒功率):PD 反馈闭环调电流,把输出锁住(更工程量产)

本小节一句话:不是少用电,而是同样输出少浪费。

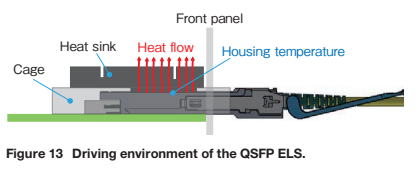

结论先行:在风冷 cage 场景里,QSFP 顶部才是主要散热出口,因此把 housing 温度定义为顶部表面温度是合理的。

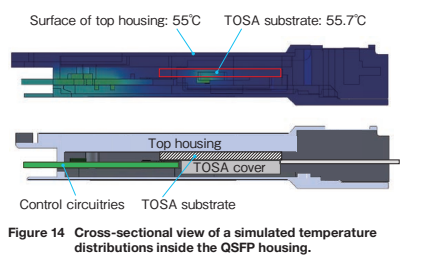

图13描述了 air-cooling 环境:QSFP 插入带顶部热沉的 cage 后,

顶部表面与热沉热连接

为了减小 housing 温度与 TOSA case 温度差异,作者强调:

TOSA 的底面应贴到 QSFP 顶盖内侧(热阻最小)

图14 的热仿真在 housing=55℃、全通道 300 mA 条件下给出:

TOSA case 温升约 0.7℃

文中另提可抑制到 1.4℃

0.7℃可能对应某位置/理想贴合假设

1.4℃更像保守条件(局部最高温升或接触热阻更差的假设)

本小节一句话:热路径短,是无TEC还能在 55℃跑起来的基础。

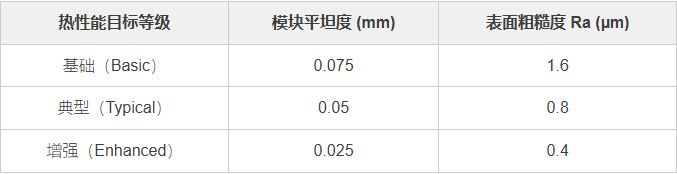

OIF 协议对与热沉接触的上下表面壳体提出粗糙度与平坦度要求。出光越大(功耗越高),越倾向选 Typical/Enhanced:

工程解释:

平坦度:决定贴不贴得上(宏观翘曲会导致局部不接触)

粗糙度:决定贴上后导得好不好(微观峰谷导致真实接触面积小,需要压力+TIM填谷)

平坦度决定能不能贴上,粗糙度决定贴上后导得好不好

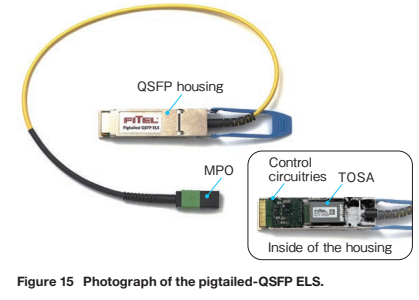

图15 给出 pigtailed-QSFP ELS 实物:TOSA + 控制板装入 QSFP,8 路 PMF 输出到 12 芯 MPO。

图16 给出 MT 插芯端面与角度结果:各通道角误差控制在 0.1–1.6°范围,PER 全通道 >20 dB。

PER 本文暂保留结论:当角误差压到 1–2°量级,PER 往往进入底噪主导区,角度与 PER 不再强单调相关。

这个数据初看与之前写的一篇有矛盾(角度越大,PER越小),后面再单独开一篇讲。

从外置光源到FAU:高双折射光纤轴向偏差的PER代价

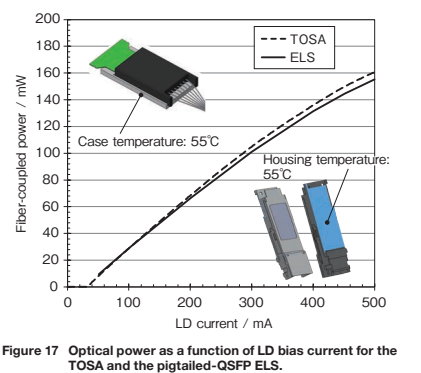

图17 给出在 TOSA case=55℃、housing=55℃ 条件下,

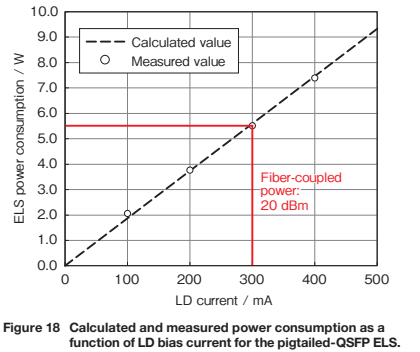

图18 给出功耗随 LD 偏置电流变化的计算与实测对比,二者吻合良好。

在 housing=55℃、全通道 300 mA 获得 >100 mW(20 dBm) 时:

实测整机功耗:5.6 W

总光功率:0.8 W

模块级 PCE ≈ 0.8/5.6 = 14.3%

本节一句话:图17(热闭环)+ 图18(电闭环)共同把 14.3% 模块级PCE做实。

论文给出两层效率闭环:

TOS级(光源发动机)

模块级(可部署 QSFP ELS)

模块级低于 TOS级的差值主要来自:

DC/DC 转换损耗

控制/监控电路损耗

系统互连与结构带来的额外损耗

参考文章: 封装与光学

您好,可以免费咨询技术客服[Daisy]

筱晓(上海)光子技术有限公司

欢迎大家给我们留言,私信我们会详细解答,分享产品链接给您。

免责声明:

资讯内容来源于互联网,不代表本网站及新媒体平台赞同其观点和对其真实性负责。如对文、图等版权问题存在异议的,请联系我们将协调给予删除处理。行业资讯仅供参考,不存在竞争的经济利益。